Q.1) What is D type flip-flop?

Answer) The D type flip-flop has one data input 'D' and a clock input. The circuit edge triggers on.the clock input. The flip-flop also has two outputs Q and not(Q). The operation of the D type flip-flop is as follows:

Any input appearing (present state) at the input D, will be produced at the output Q in next clock cycle

Example : If in the current time D = 0 and Q = 1, the next state will be D = (0/1) and Q = 0.

Truth Table for D Flip Flop.

Q.2) Draw the excitation table for D - flip flop.

Answer) From the truth table, we can see that,

When Q retains it state from '0' to '0' or changes from '1' to '0', the value of D is '0'.

When Q retains it state from '1' to '1' or changes from '0' to '1' , the value of D is '1'.

Excitation table for D flip flop.

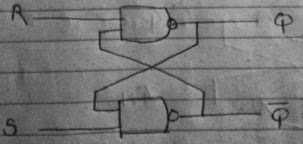

Q.3) Draw the circuit diagram of D - flip flop.

Answer) The circuit diagram for D flip flop can be easily drawn by converting the S-R flip flop into D flip flop. For converting one flip flop to another, a truth table is prepared by combining the excitation tables for both the flops. The given flop (in this case S-R flip flop) acts as outputs and flop to be derived (in this case D flip flop) along with current output and next state output acts as inputs.

Combined truth table for converting S-R flip flop into D flip flop.

K-Map Simplification

D Flip Flop using S-R Flip Flop.

Q.4) Convert D flip flop into S-R flip flop.

Answer) In this case,

Given flop : D flip flop (output)

Flop to be derived : S-R flip flop (input)

Combined truth table for converting D flip flop into S-R flip flop.

K-Map Simplification

S-R Flip Flop using D Flip Flop.