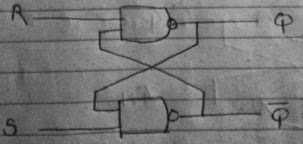

Q.1) Explain S-R Latch using NAND gates.

Answer) Latch is a sequential logic circuit which checks all its inputs continuously and will change its output as soon as the input changes without waiting for the clock signal. Generally an enable signal is provided for a latch. When the enable signal is active, the output will change as soon as there is change in input.

It has two outputs Q and not(Q) which are complements of each other.

The boolean equation for the outputs can be expressed as follows :

Q = not(R.not(Q))

not(Q) = not(S.Q)

I) S = 0, R = 0 (Race Condition)

Substituting the value of S and R in the above equations, we get both Q and not(Q) as 1. This is an indeterminate state and should be avoided.

II) S = 0, R = 1 (Reset Condition)

Since, S = 0, it forces not(Q) to be 1 and R = 1 forces Q = 0.

III) S = 1, R = 0 (Set Condition)

In this case, R = 0 forces the Q = 1 and S = 1 forces not(Q) = 0.

IV) S = 1, R = 1 (No change)

Substituting the values of S and R in the above equation, we get,

Q = Q and not(Q) = not(Q), hence there is no change in the outputs.

Q.2) Explain positive edge triggered S-R flip flop.

Answer) The S-R flip flop consists of a differentiator circuit and a S-R gated latch. C-R1 acts as a differentiator and converts the rectangular clock pulses into positive and negative spikes. The diode acts as a rectifying diode and allows only the positive spikes to pass through, blocking the negative spikes.

Q.3) Draw the excitation table for S-R flip flop.

Answer) From the above truth table, we can infer following points :

- When Q retains state '0', we have two conditions S = R = '0' and S = '0'; R = '1', hence to retain state '1', S = '0' and R = 'x'

- When Q changes from 0' to '1', S = '1' ; R = '0'

- When Q changes from '1' to '0', S = '0' ; R = '1'.

- When Q retains state '1' , we have two conditions S = R = '0' and S = '1'; R = '0', hence to retain state '1' , S='x' and R = '0'.

Q.4) Explain race condition.

Answer) Race condition occurs when both S and R input of latch becomes '0'. When any one input to a NAND gate is '0', its output becomes '1'. Thus both the outputs will try to become '1', hence it is called race condition.

No comments:

Post a Comment